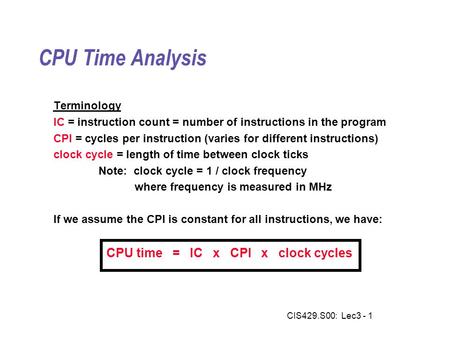

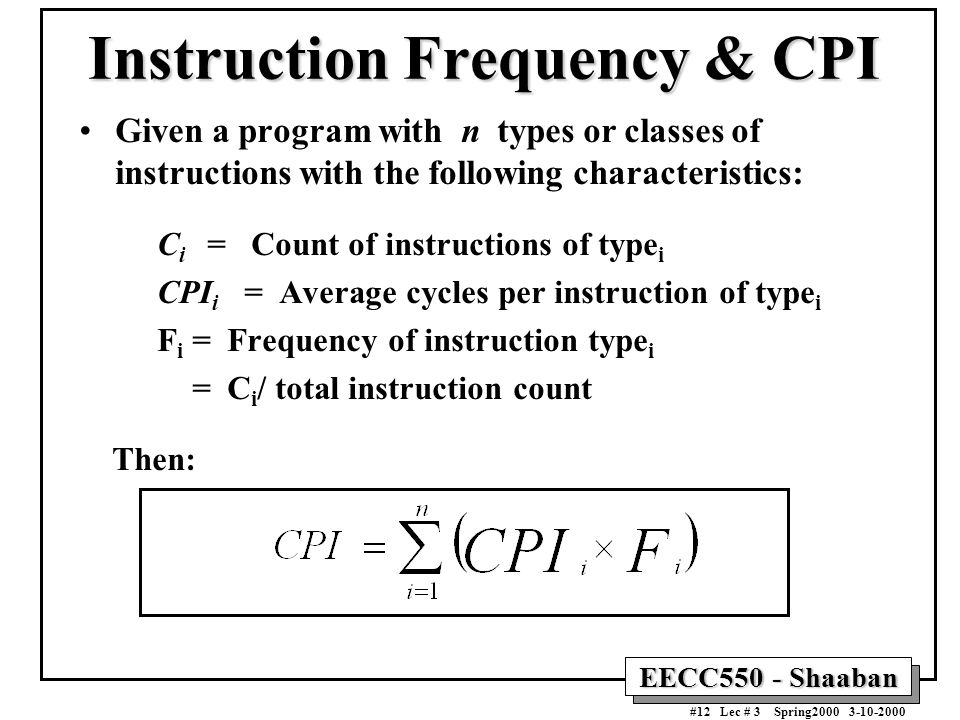

Average CPI for the program. IPC stands for instructions per cycleclock.

Cycles Per Instruction An Overview Sciencedirect Topics

The computation of instructions per cycles is a measure of the performance of an architecture and a basis of comparison all other things being equal.

Instructions per clock. Instructions Clock Cycles IPS ------------ x ------------ Clock Cycles Seconds. To get more performance you need to up the clock. That will make for a double-digit percent Instructions Per Clock IPC increase Intel claims and it says that will help it deliver amazing performance and flexibility to meet a range of needs.

IPC can be used to compare two designs for the same instruction set architecture as in the question youre asking comparing two design alternatives for a MIPS architecture. For instruction-dense code 10 is going to be mediocre. HttpgooglLuttfMIs the clock frequency the main gauge of a CPUs performance.

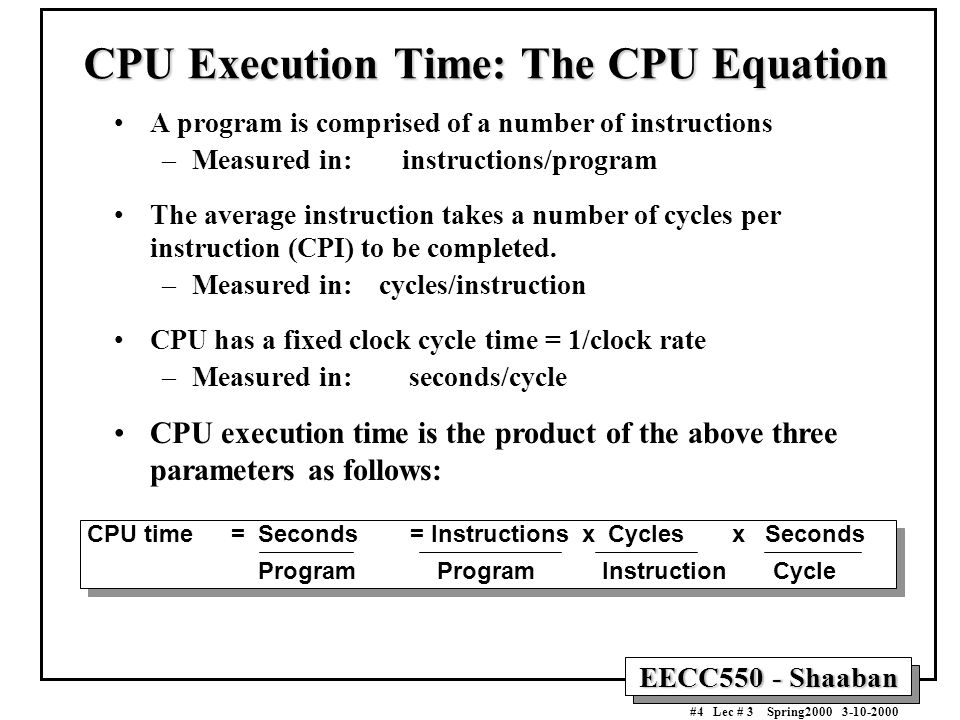

CPU time Instruction count x CPI x Clock cycle 10000000 x 25 x 1 clock rate 10000000 x 25 x 5x10-9 0125 seconds. We can reason about IPC for instruction-dense code. External clock T0CKI pin.

Extend the count period 16 for applications 1 and 2. So this means that it would take 4 clock cycles to execute an instruction which is 025 instructions per clock. In older architectures the number of cycles was fixed nowadays the number of cycles per instruction usually depends on various factors cache hitmiss branch prediction etc.

How could CPU execute more than one instruction per clock cycle. A superscalar CPU architecture implements a form of parallelism called instruction-level parallelism within a single processor. Internal clock f OSC 4 Pre-scale16.

This gives you the middle part of the provided formula. Preload Timer0 with initial value and count up to 256. And since 1 AB BA.

We know what 40 instructions per cycle means. Timer mode using instruction clock. There are tables to look up that stuff.

Clear Timer0 initially and read count later to measure time elapsed. CPU clock rate. Basically we have a measure of how superscalar wide the processor is.

CPUs are like factories having machines that do different tasks form a production line. While clock speed tells you how many cycles a CPU can complete in. Timer mode using instruction clock with pre-scale.

1 Once upon a time there were a lot of arguments about CPU efficiency often expressed as IPC or Instructions Per Clock with bigger better. Besides the actual power consumption overhead of supporting branch prediction and speculative execution eg prediction structures support for check pointing increased run-time state there is also the issue of. These modern processors have multiple execution units per core as.

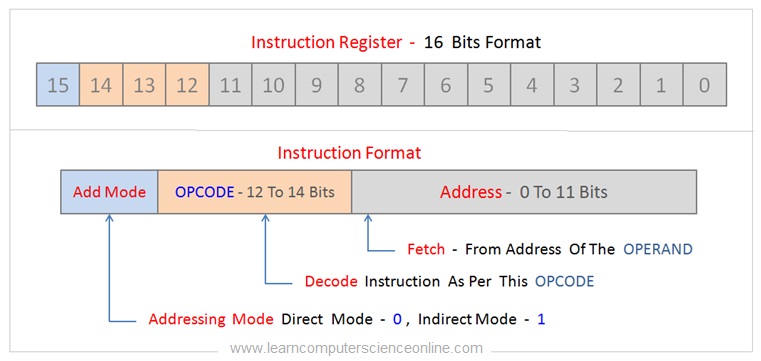

Although they are necessary in order to keep functional units busy and to have high Instructions Per Cycle IPC branch predictors and speculative activity approach are fairly power hungry. In a CISC architecture x86 68000 VAX one instruction is powerful but it takes multiple cycles to process. Clock Cycles Clock Cycles CPI ------------ and Clock Rate ------------ Instructions Seconds.

A On any given date vendors might have different clock rates and performance is affected by clock rates. It therefore allows faster CPU throughput than would otherwise be possible at a given clock rate. TEHRAN FNA- AMD is still claiming a 40 improvement in instructions per clock for Zen but now the company has actually demonstrated the previously announced 8-core 16-thread Summit Ridge system - and is showing it outperforming an Intel Broadwell-E processor at least in certain applications at the same clock speed.

Theres a common beat the core clock but as they do different things you may be able to send multiple instructions down the line that will be handled on separate paths through the factory at the same time. No because it matters how many instructions the CPU can exe. Tech Bytes and a subject matter expert explain what Instructions Per Clock IPC is and the architecture enhancements and IPC improvements in the.

This tells you how many things a CPU can do in one cycle. Clock cycle C 5x10-9 seconds What is the execution time for this program.

Understanding The Instruction Pipeline Tech Decoded Powered By Intel

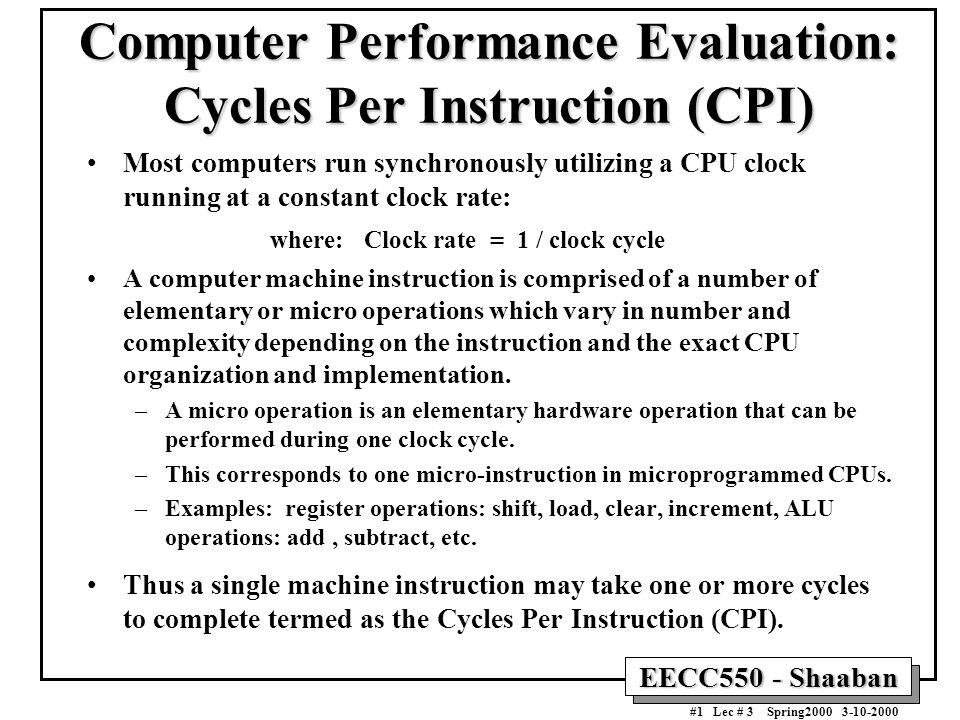

Computer Performance Evaluation Cycles Per Instruction Cpi Ppt Video Online Download

Computer Performance Evaluation Cycles Per Instruction Cpi Ppt Video Online Download

How Many Operations Per Second Can A Computer Do How Is It Related To Ghz Quora

What Is Mips Million Of Instructions Per Second Geeksforgeeks

Computer Performance Evaluation Cycles Per Instruction Cpi Ppt Video Online Download

Organization Of Computer Systems Pipelining

Computer Performance Evaluation Cycles Per Instruction Cpi Ppt Video Online Download

Arm Vs X86 Key Differences Explained Youtube

How Many Operations Per Second Can A Computer Do How Is It Related To Ghz Quora

Multiprocessing At A Glance I Processors And Cores Adoredtv

Understanding The Instruction Pipeline Tech Decoded Powered By Intel

Instruction Cycle Explained Fetch Decode Execute Cycle Step By Step

Cycles Per Instruction An Overview Sciencedirect Topics

Cycles Per Instruction An Overview Sciencedirect Topics

Understanding The Instruction Pipeline Tech Decoded Powered By Intel

Instructions Per Cycle An Overview Sciencedirect Topics

How Many Operations Per Second Can A Computer Do How Is It Related To Ghz Quora